# **Power Optimization Methodologies for Digital FIR Decimation Filters**

Dissertation zur Erlangung des Doktorgrades der Technischen Fakultät der Albert-Ludwigs-Universität Freiburg

**Ahmed Shahein**

2014

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doktor-Ingenieur in Microsystems Engineering

according to the examination regulations at the University of Freiburg for the Ph.D. in Microsystems Engineering of 10.05.2000.

Department of Microsystems Engineering – IMTEK Fritz Huettinger Chair of Microelectronics University of Freiburg Freiburg im Breisgau, Germany

Dean:

Referees:

Prof. Dr.-Ing Yiannos Manoli

Prof. Dr.-Ing. Yiannos Manoli Fritz Huettinger Chair of Microelectronics Prof. Dr. Leonhard Reindl Laboratory for Electrical Instrumentation

| Declaration | according to $\$5(2f)$ of the examination regulations                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|             | I hereby confirm to have written the following dissertation<br>on my own, not having used any other sources or resources<br>than those listed. |

|             | Freiburg, July 10, 2014                                                                                                                        |

|             | Ahmed Shahein                                                                                                                                  |

To my beloved parents - my father and best friend Prof. Dr.-Eng. Hussein Shahein and my mother Eng. Magda Farouk. Who gave me all the support and motivation I need.

# Contents

| At  | ostrac         | t                                            | 1  |

|-----|----------------|----------------------------------------------|----|

| Ζu  | ısamr          | nenfassung                                   | 3  |

| Lis | st of <i>i</i> | Abbreviations                                | 5  |

| Lis | st of S        | Symbols                                      | 7  |

| 1.  | Ove            |                                              | 9  |

|     | 1.1.           | Motivation                                   | 9  |

|     | 1.2.           | Outline                                      | 10 |

|     | 1.3.           | Contributions                                | 10 |

|     | 1.4.           | Deliverables                                 | 11 |

| 2.  | Sign           | na Delta ADCs                                | 13 |

|     | 2.1.           | Introduction                                 | 13 |

|     | 2.2.           | Need of Data Converters                      | 13 |

|     | 2.3.           | Survey of Analog-to-Digital Converters       | 13 |

|     | 2.4.           | Sigma Delta ADC                              | 14 |

|     |                | 2.4.1. Sigma Delta Modulator Classifications | 15 |

|     |                | 2.4.2. Sigma Delta Decimation Filter         | 17 |

|     | 2.5.           | Decimation Filter Design Parameters          | 22 |

|     | 2.6.           | Summary                                      | 23 |

| 3.  | Low            | Power Design Aspects                         | 25 |

|     | 3.1.           | Introduction                                 | 25 |

|     | 3.2.           | Sources of Power Dissipation                 | 26 |

|     | 3.3.           | Power Optimization Approaches                | 28 |

|     | 3.4.           | Power Analysis                               | 29 |

|     | 3.5.           | Summary                                      | 30 |

| 4.  | Algo           | rithmic System Level Terminology             | 33 |

|     |                | Introduction                                 | 33 |

|     | 4.2.           | FIR Filter Conventions                       | 33 |

|     |                | 4.2.1. Coefficient Quantization              | 34 |

|     |                | 4.2.2. Coefficient Scaling                   | 35 |

|     |                | 4.2.3. Coefficient Representation            | 37 |

|     | 4.3.           | Bounded Search Space                         | 39 |

i

|    | 4.4.<br>4.5. |                                                                                                                                                                          | $\frac{39}{46}$ |

|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|    |              |                                                                                                                                                                          | 46              |

|    |              |                                                                                                                                                                          | 48              |

|    |              | 4.5.3. Hybrid                                                                                                                                                            | 48              |

| 5. | -            |                                                                                                                                                                          | 51              |

|    | 5.1.         |                                                                                                                                                                          | 51              |

|    | 5.2.         |                                                                                                                                                                          | 52              |

|    | 5.3.         |                                                                                                                                                                          | 54              |

|    | 5.4.         |                                                                                                                                                                          | 56              |

|    | 5.5.         | 0 0                                                                                                                                                                      | 58              |

|    |              |                                                                                                                                                                          | 59              |

|    |              |                                                                                                                                                                          | 60              |

|    |              | 1 0                                                                                                                                                                      | 61              |

|    |              | 1                                                                                                                                                                        | 64              |

|    |              | 5.5.5. Performance Evaluation and Results                                                                                                                                | 67              |

|    | 5.6.         | Common Sub-expression Elimination                                                                                                                                        | 79              |

|    | 5.7.         | Summary                                                                                                                                                                  | 87              |

| 6. | Arcł         | nitectural System Level Power Optimization                                                                                                                               | 89              |

|    | 6.1.         |                                                                                                                                                                          | 89              |

|    | 6.2.         | Combined DF and TF Architectures                                                                                                                                         | 89              |

|    |              | J                                                                                                                                                                        | 90              |

|    |              |                                                                                                                                                                          | 91              |

|    |              |                                                                                                                                                                          | 95              |

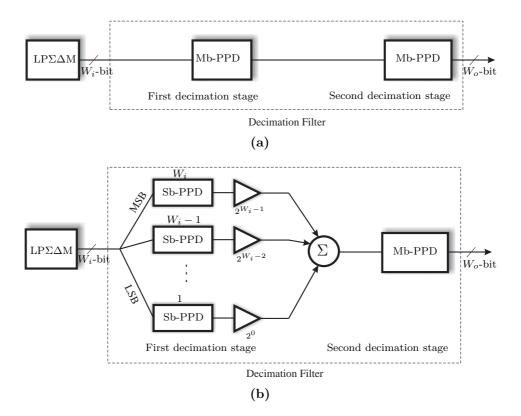

|    | 6.3.         | Implementing Mb using Sb Decimation Filter                                                                                                                               | 95              |

|    | 6.4.         | Summary                                                                                                                                                                  | 96              |

| 7. | Desi         | ign and Implementation Procedure                                                                                                                                         | 99              |

|    | 7.1.         | Introduction                                                                                                                                                             | 99              |

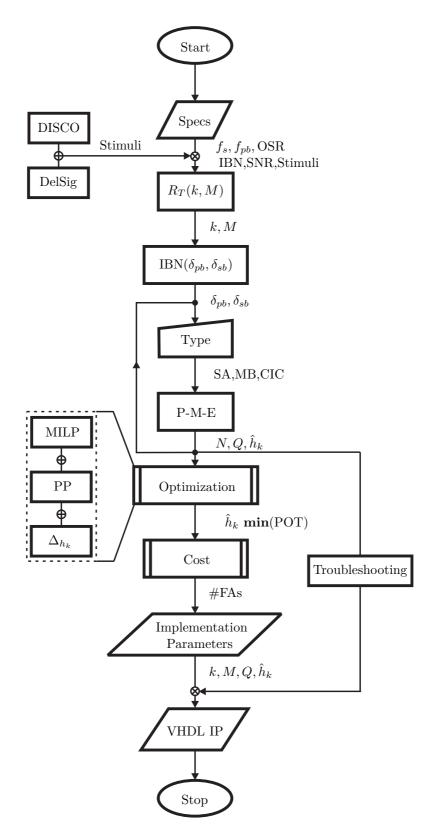

|    | 7.2.         | Multi-Stage Decimation Toolbox                                                                                                                                           | 99              |

|    |              | 7.2.1. $k$ and $M$ Calculations $\ldots \ldots \ldots$   | 02              |

|    |              | 7.2.2. $\delta_{pb}$ and $\delta_{sb}$ Calculations                                                                                                                      | 02              |

|    |              | 7.2.3. $h_k$ and $Q$ Calculations $\ldots \ldots \ldots$ | 03              |

|    |              | 7.2.4. Coefficient Optimization                                                                                                                                          | 10              |

|    |              | 7.2.5. Cost Estimation $\ldots \ldots \ldots$            | 10              |

|    | 7.3.         | Troubleshooting and Verification                                                                                                                                         | 12              |

|    | 7.4.         | Design Example                                                                                                                                                           | 13              |

|    | 7.5.         | MSD-toolbox Evaluation                                                                                                                                                   | 19              |

|    | 7.6.         | VHDL IPs                                                                                                                                                                 | 21              |

|    |              | 7.6.1. Tools Chain                                                                                                                                                       | 21              |

|    |              | 7.6.2. Polyphase Decimation Filter                                                                                                                                       | 23              |

|    |              | 7.6.3. Cascaded Integrator Comb Filter                                                                                                                                   | 32              |

|    | 7.7.         | Summary                                                                                                                                                                  |                 |

| 8.  | RTL               | Power Optimization                         | 137 |

|-----|-------------------|--------------------------------------------|-----|

|     | 8.1.              | Introduction                               |     |

|     | 8.2.              | Problem Notations                          |     |

|     | 8.3.              | Discrepancy                                |     |

|     | 8.4.              | Proposed Nested Constant Multiplier        |     |

|     |                   | 8.4.1. Theory                              |     |

|     |                   | 8.4.2. Implementation                      |     |

|     |                   | 8.4.3. Nested Multiplication Driven by CSE |     |

|     | 8.5.              | RTL Modeling                               |     |

|     | 8.6.              | Summary                                    | 146 |

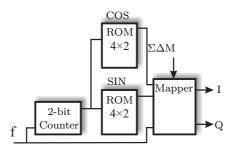

| 9.  | Digi              | tal Front End                              | 149 |

|     | 9.1.              | Introduction                               | 149 |

|     | 9.2.              | Design Specifications                      |     |

|     | 9.3.              | Proposed DFE                               | 150 |

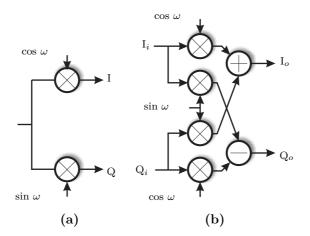

|     | 9.4.              | Digital Down Converter                     |     |

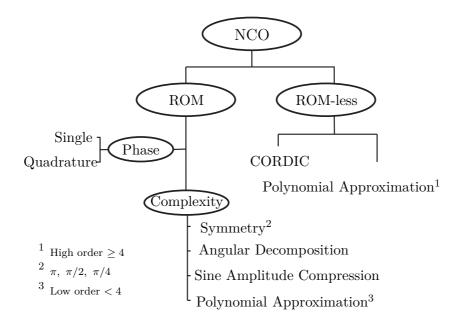

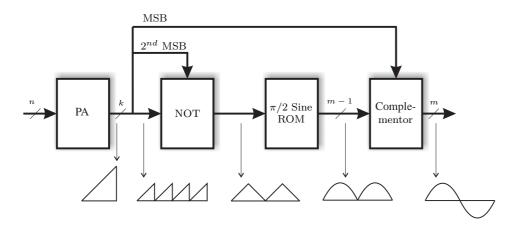

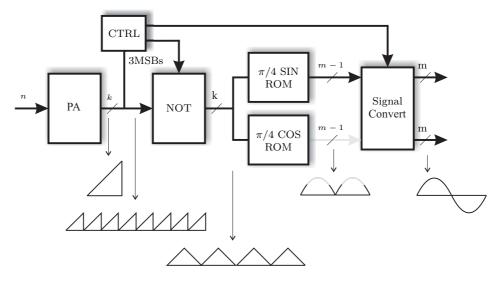

|     | 9.5.              | Numerical Controlled Oscillator            | 153 |

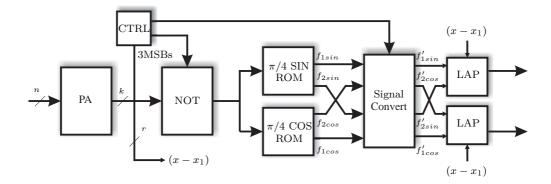

|     |                   | 9.5.1. Sinusoidal Symmetry NCO Topologies  |     |

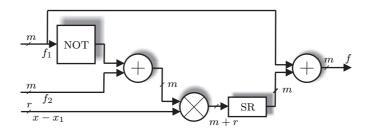

|     |                   | 9.5.2. Performance Enhancement Criteria    | 157 |

|     |                   | 9.5.3. Modeling and Analysis               |     |

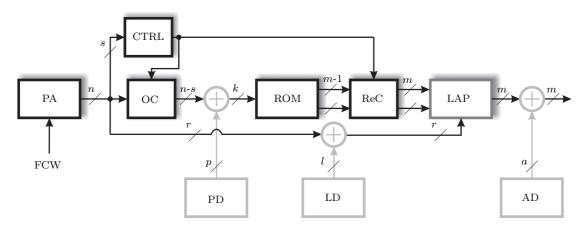

|     |                   | 9.5.4. Proposed Design Scheme              |     |

|     |                   | 9.5.5. Power Analysis                      |     |

|     | 9.6.              | Decimation Filters                         |     |

|     |                   | 9.6.1. CIC Decimation Filter               |     |

|     |                   | 9.6.2. FIR Polyphase Decimation Filter     |     |

|     | 9.7.              | Power Simulation and Analysis              | 168 |

|     | 9.8.              | Summary                                    | 170 |

| 10  | Con               | clusion and Outlook                        | 171 |

| Bil | oliogr            | raphy                                      | 175 |

| Lis | t of              | Figures                                    | 187 |

| Lis | t of <sup>.</sup> | Tables                                     | 191 |

| Ар  | pend              | lix                                        | 193 |

| Α.  | Polv              | nomial Programming                         | 193 |

|     |                   | insampling                                 | 195 |

|     |                   | mannhung                                   |     |

|     | lex               |                                            | 199 |

| Ac  | know              | ledgements                                 | 201 |

## Abstract

There is a trend to replace analog by digital components, resulting in digital filters to become ubiquitous in signal processing applications. Especially for digital finite impulse response (FIR) filters, the power consumption though can be considerable and become a limiting factor in numerous scenarios, e.g., mobile and automotive applications. One major focus of this research work therefore is the optimization of power consumption in digital FIR filters, both on system and register transfer level (RTL).

The practical design tools implemented within the framework of this thesis include a consolidated toolbox for design, optimization and RTL implementation of digital FIR decimation filters, and a set of RTL-based soft IPs for several digital FIR filter topologies. The power optimization in this tool-chain is based on an optimization of filter coefficients, a beneficial combination of filter topologies and an improved multiplier architecture.

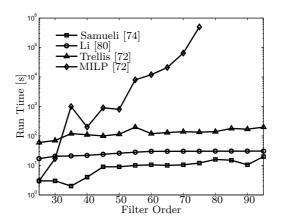

The complexity and therewith power consumption of hardwired multipliers in FIR filters is directly related to the number of ones in the binary representation of the filter coefficients. The optimization of filter coefficients is achieved by reducing the number of ones. A heuristic algorithm to minimize this coefficient cost is presented. The proposed algorithm achieves a remarkable reduction in the computation time compared to the state-of-the-art algorithms due to an extensive preprocessing analysis on the filter coefficients and a novel allocation scheme. A reduction in the run-time by a factor of 400 is achieved by the presented algorithm compared to the state-of-the-art algorithms.

The improved filter topologies are accomplished through a power aware combination criterion for different FIR digital filter topologies. A reduction in power dissipation up to 15% is achieved by the proposed criterion compared to the conventional filter architecture.

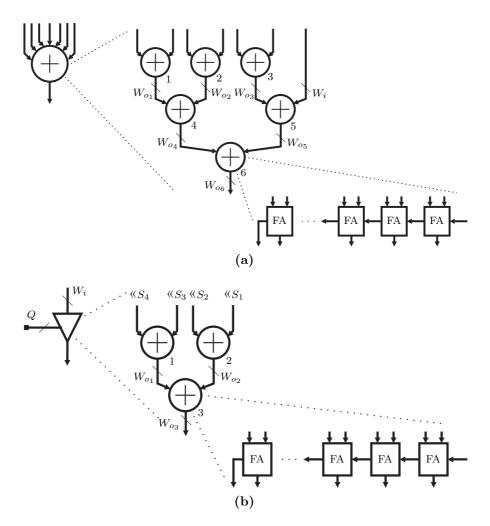

An improved multiplier architecture is proposed implementing a novel encoding scheme for shift-and-add multiplier-less architectures. A reduction in hardware cost by 25% is achieved compared to the state-of-the-art scheme.

The second main focus of this work is the power optimization of digital receivers, which incorporate complex FIR filters as discussed above, but furthermore require

numerically controlled oscillators (NCOs) and a careful topological design. A comprehensive study for ROM-based NCOs is carried out. The study employs various state-of-the-art methodologies for performance enhancement such as symmetry, dithering and linear approximation. The result is a design scheme for calculating the implementation parameters for a low complexity ROM-based NCO architecture.

Finally, a power optimized digital front end for a tunable narrow band FM digital receiver is designed and synthesized in a 130 nm CMOS technology. A power reduction by 60% is achieved by the proposed design compared to the conventional architecture.

## Zusammenfassung

Es ist der Trend zu beobachten, dass analoge Komponenten zunehmend durch digitale ersetzt werden. Digitale Filter für die Signalverarbeitung in unterschiedlichen Anwendungsfeldern sind dadurch allgegenwärtig geworden. Insbesondere die Leistungsaufnahme von digitalen FIR (finite impulse response)-Filtern kann allerdings erheblich sein, was die Anwendbarkeit in vielen Fällen einschränken kann, z.B. in mobilen Anwendungen und in der Automobiltechnik. Ein Schwerpunkt dieser Forschungsarbeit ist daher die Optimierung der Leistungsaufnahme in digitalen FIR-Filtern, sowohl auf der System-, wie auch auf der Register-Transfer-Ebene (register transfer level, RTL).

Die hierfür realisierten Entwurfswerkzeuge beinhalten einen umfassenden Satz an Werkzeugen für das Design, die Optimierung und RTL-Implementierung von digitalen FIR Dezimationsfiltern, und einen Satz von RTL-basierten soft-IPs für unterschiedliche, digitale FIR-Filter-Topologien. Die Optimierung der Leistungsaufnahme in diesen Werkzeugen erfolgt mittels einer Optimierung der Filterkoeffizienten, einer vorteilhaften Kombination von Filtertopologien und einer verbesserten Architektur für die verwendeten Multiplizierer.

Die Komplexität und damit auch Leistungsaufnahme der festverdrahteten Multiplizierer in FIR Filtern steht in direktem Bezug zu der Anzahl an Einsen in der Binärdarstellung der Filterkoeffizienten. Die Optimierung der Filterkoeffizienten erfolgt durch eine Reduzierung der Anzahl an Einsen. Es wird ein heuristischer Algorithmus zur Minimierung dieses Koeffizienten-Kostenfaktors vorgestellt. Der vorgeschlagene Algorithmus erreicht eine bemerkenswerte Verringerung der Rechenzeit verglichen mit anderen State-of-the-Art Algorithmen, was durch eine eingehende Analyse der Filterkoeffizienten vor der eigentlichen Berechnung und einen neuartigen Ablauf der Koeffizientenzuordnung erreicht wird. Die erzielte Verbesserung der Laufzeit im Vergleich zu anderen State-of-the-Art Algorithmen liegt bei einem Faktor 400.

Eine Verbesserung der Filterstruktur wird durch ein Auswahlverfahren für unterschiedliche digitale FIR Filtertopologien erzielt, das speziell im Hinblick auf die Leistungsaufnahme entwickelt wurde. Die Leistungsaufnahme kann durch das vorgeschlagene Verfahren im Vergleich zu einer konventionellen Filterstruktur um bis zu 15% reduziert werden.

Es wird eine verbesserte Architektur für Multiplizierer vorgestellt, die einen neuartigen Kodierungsansatz für multipliziererlose Shift-and-Add Architekturen verwendet. Hierdurch wird eine Reduktion des Hardwareaufwands um 25\% im Vergleich zu bestehenden State-of-the-Art Ansätzen erzielt.

Der zweite Schwerpunkt dieser Arbeit liegt bei der Optimierung der Leistungsaufnahme von digitalen Receivern, die komplexe FIR Filter beinhalten und damit ein Anwendungsfall für die bereits diskutieren Verfahren darstellen, darüber hinaus aber auch numerisch kontrollierte Oszillatoren (numerically controlled oscillators, NCOs) benötigen und eine wohlüberlegte topologische Auslegung erfordern. Es erfolgt eine umfassende Betrachtung von ROM-basierten NCOs, welche unterschiedliche State-of-the-Art Ansätze zur Verbesserung der Leistungsfähigkeit beinhaltet, insbesondere die Ausnutzung von Symmetrien, Dithering und lineare Approximation. Als Ergebnis ergibt sich ein Designansatz, der eine Berechnung der Parameter für einen ROM-basierten NCO mit möglichst geringer Komplexität erlaubt.

Abschließend wird ein leistungsoptimiertes digitales Front-End für einen schmalbandigen, abstimmbaren digitalen FM Receiver in einer 130 nm CMOS Technologie entworfen und synthetisiert. Verglichen mit der konventionellen Architektur wird dabei eine Verbesserung der Leistungsaufnahme um 60% erzielt.

### List of Abbreviations

AAF Anti-Aliasing Filter AD ADder cell ADC Analog-to-Digital Converter Application Specific Integrated Circuits ASIC BW Band Width CIC Cascaded Integrator Comb CMOS Complementary Metal-Oxide-Semiconductor CTContinuous Time DAC Digital-to-Analog Converter DDC Digital Down Converter DDS Direct Digital Synthesizer DF Direct-Form DFE Digital Front End DFF Delay Flip Flop DL DeLay cell DSP Digital Signal Processing DT Discrete Time Electronic Design Automation EDA FA Full-Adder FBFeed-back FCW Frequency Control Word  $\mathbf{FF}$ Feed-forward FIR Finite Impulse Response FPGA Field Programmable Gate Array HB Half-Band HVL Hardware Verification Language IBN In-Band Noise IF Intermediate Frequency IIR Infinite Impulse Response IP Intellectual Property LAP Linear APproximation LPF LowPass Filter LSB Least Significant Bit LUT Look-Up-Table MA Multiplier Adder Multi-Band MB

Mb Multi-bit

| MILP                | Mixed Integer Linear Programming  |

|---------------------|-----------------------------------|

| MOA                 | Multi-Operand Adder               |

| MSB                 | Most Significant Bit              |

| MU                  | MUltiplier cell                   |

| NB                  | Narrow-band                       |

| NCO                 | Numerically Controlled Oscillator |

| OSR                 | OverSampling Ratio                |

| P-M-E               | Parks-McClellan Equiripple        |

| POT                 | Power-Of-Two                      |

| PP                  | Polynomial Programming            |

| PPD                 | PolyPhase Decomposition           |

| PSD                 | Power Spectral Density            |

| RCA                 | Ripple Carry Adder                |

| $\operatorname{RF}$ | Radio Frequency                   |

| ROM                 | Read Only Memory                  |

| RTL                 | Register Transfer Level           |

| SA                  | Structural Adder                  |

| $\operatorname{Sb}$ | Single-bit                        |

| SDC                 | Synopsys Design Constraints       |

| SDF                 | Standard Delay Format             |

| SFDR                | Spurious-Free Dynamic Ratio       |

| SNR                 | Signal-to-Noise Ratio             |

| $\mathrm{TF}$       | Transposed-Form                   |

| Tcl                 | Tool command language             |

| VCD                 | Value Change Dump                 |

| VHDL                |                                   |

| $\Sigma \Delta M$   | Sigma Delta Modulator             |

|                     |                                   |

### List of Symbols

- $f_s$  Sampling frequency in Hz

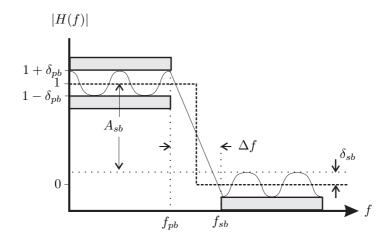

- $f_{pb}$  Passband frequency in Hz

- $f_{sb}$  Stopband frequency in Hz

- $\Delta_f$  Transition bandwidth in Hz

- $f_c$  Center frequency

- $f_B$  Base-band frequency

- $f_{signal}$  Signal frequency

- $\delta f$  Channel band-width

- $\omega_s$  Sampling frequency in rad/s

- $\omega_{pb}$  Passband frequency in rad/s

- $\omega_{sb}$  Stopband frequency in rad/s

- $\Delta_{\omega}$  Transition bandwidth in rad/s

- $\delta_{pb}$  Passband ripples

- $\delta_{sb}$  Stopband ripples

- $A_{sb}$  Stopband attenuation

- N Filter order

- Q Quantization bit-width

- k Number of decimation stages

- M Decimation factor

- $W_{i/o}$  Input/Output bit-width

- $R_T$  Computation effort

- $h_k$  Filter coefficients

- $\hat{h}_k$  Scaled filter coefficients

- $S_n$  Coefficient sensitivity

- $\Delta_{h_k}$  Coefficient deviation

- $U_b$  Upper bound

- $L_b$  Lower bound

- $E^i$  Elements function with *i* non-zero term

- m ROM address bit-width

- k ROM word-length

- n Phase bit-width

- r Approximation bit-width

- p Phase dithering bit-width

- a Amplitude dithering bit-width

- l Approximation dithering bit-width

### 1. Overview

The ongoing need for portable and hand-held personal communication systems has encouraged the development of low power, small size, and high performance devices. Therefore, a reliable, flexible, and efficient signal processing is required. Furthermore, due to the rapid scaling and progress of silicon CMOS technology, analog signal processing systems are replaced with their digital counterparts. Finite Impulse Response (FIR) filters are widely used in digital signal processing applications due to their stability and linear phase characteristics. Therefore, the optimized implementation of FIR filters in hardware has gained significant attention in the research community. One crucial optimization aspect is the low power design of the FIR filters, which also is the main interest of this thesis.

#### 1.1. Motivation

```

'THE WORLD AT YOUR FINGERTIP'

'THE WORLD IS BECOMING MORE DIGITAL'

```

These phrases interpret speed and mobility of data and information. What people considered as luxury a couple of decades ago becomes a necessity of life nowadays. Hand-held devices, portable communication, voice over internet protocol (VOIP), medical devices, etc., imply the rapidly growing demand for a wide range of consumer applications and medical devices with higher battery life time. Therefore low power design is an essential trend in research nowadays.

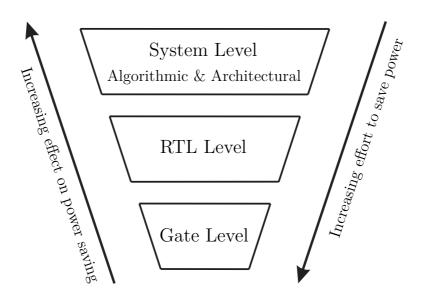

The reduction of power dissipation can be achieved on system level, register transfer level (RTL), and gate level. On the one hand, the **effort** for reducing power dissipation is increased going from system level to gate level. On the other hand, the **effect** of power reduction is maximized at the system level compared to the gate level, at least regarding dynamic power consumption. Dynamic power is the most dominant component of power consumption in digital filters. Hence, this work concentrates on power optimization methodologies on system and RTL levels.

### 1.2. Outline

- Chapter 2 reviews Sigma Delta Modulator fundamentals, classifications, and architectures.

- Chapter 3 reviews the different sources of power dissipation and the power optimization paradigm.

- Chapter 4 highlights the algorithmic system level nomenclature and the problem notation. Then the description of the proposed novel allocation scheme is given.

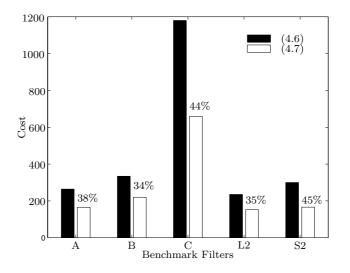

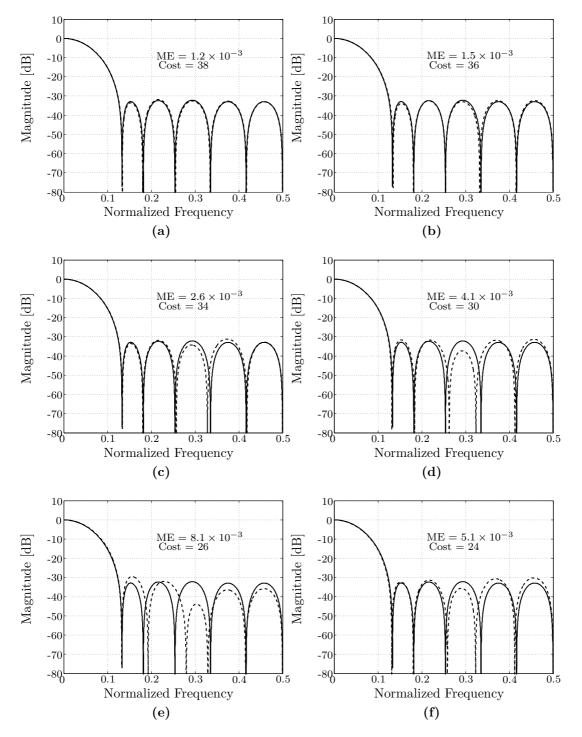

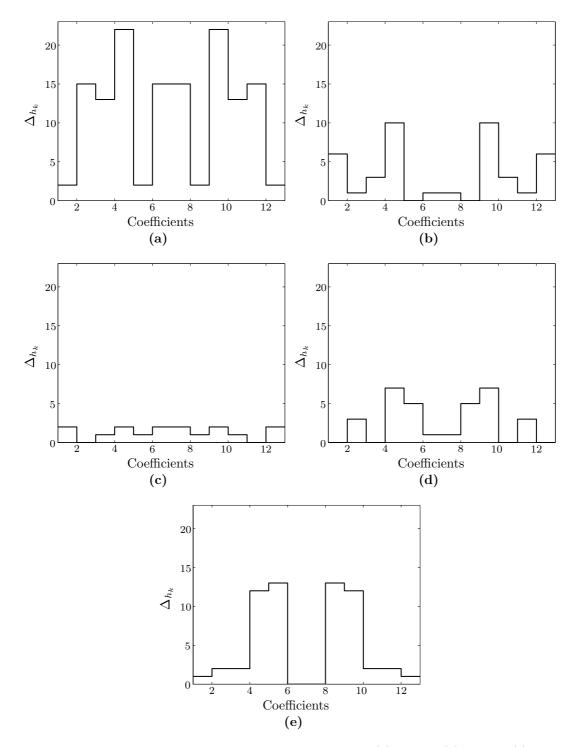

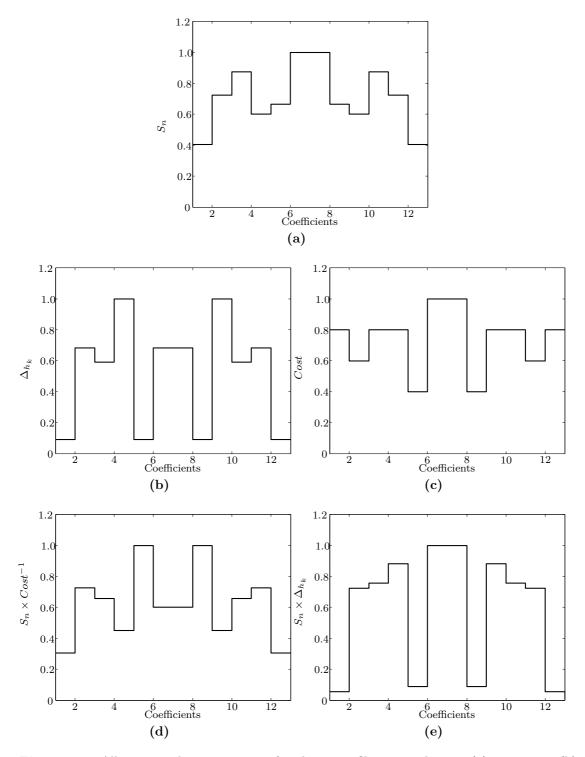

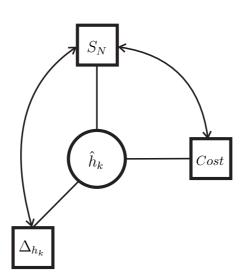

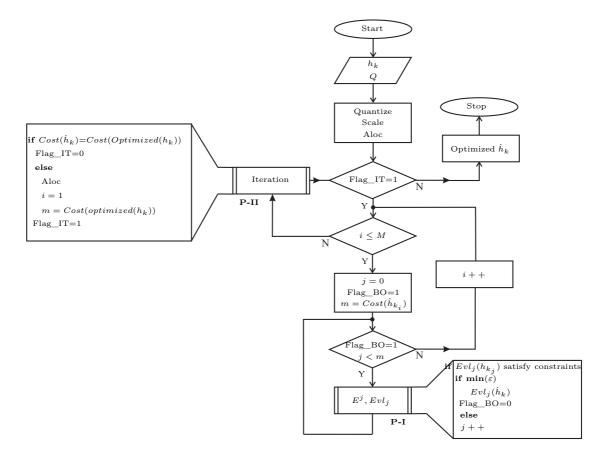

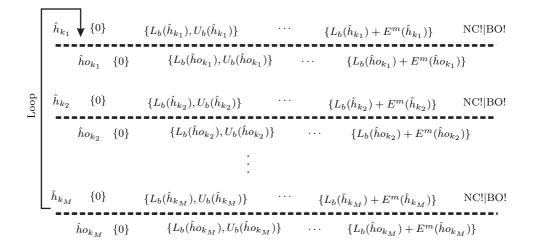

- Chapter 5 presents the proposed algorithmic optimization methodology for digital filters. The chapter starts with a graphical explanation of the problem statement. Then a detailed explanation for the proposed algorithm is given and results from the performance evaluation for a set of benchmark filters are presented.

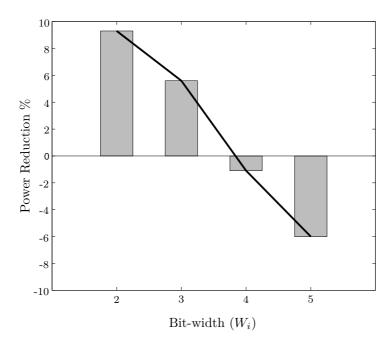

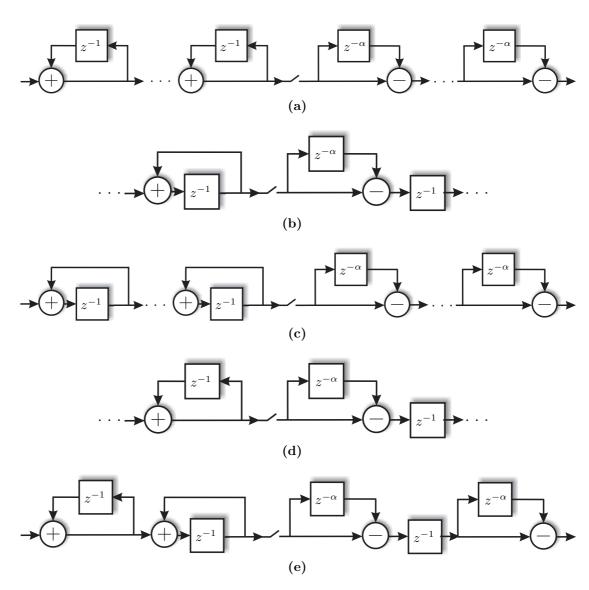

- Chapter 6 shows two methodologies for architectural power optimization. First, a power aware criterion for combining direct-form and transposedform digital filters to achieve further power reduction is presented. Then, constructing multi-bit decimation filters using single bit filters is given.

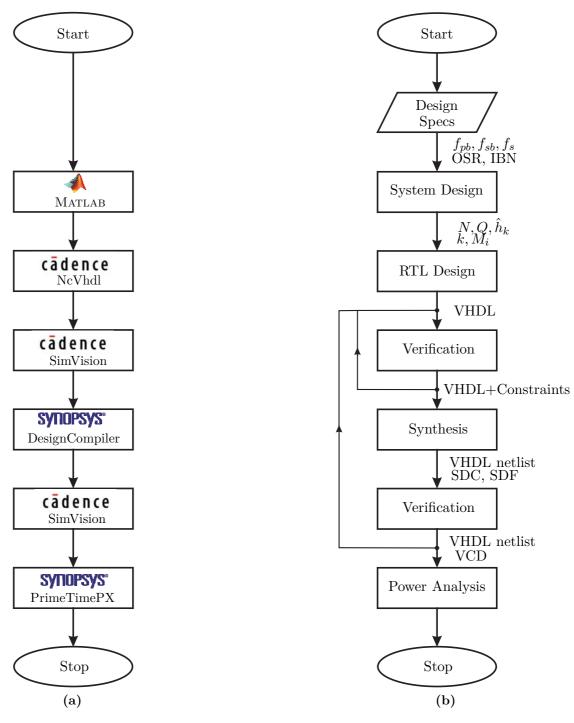

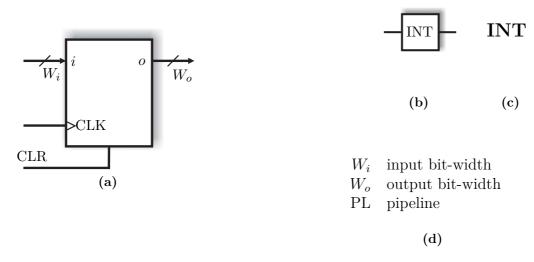

- Chapter 7 outlines the backbone assets for this work which are the design procedure and implementation models. This chapter gives a detailed explanation of the deliverables of this work which are a MATLAB toolbox and a set of RTL-based soft IPs.

- Chapter 8 describes the proposed encoding scheme for shift-and-add multipliers to reduce the internal bit-width, consequently reducing the number of full-adders employed by the multiplier.

- Chapter 9 presents the power optimized digital front end for tunable narrowband digital FM receivers.

- Chapter 10 presents the conclusion and dissertation outlook.

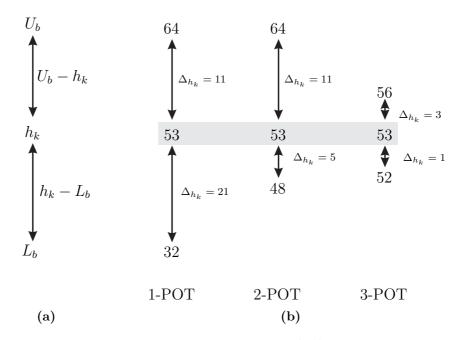

### 1.3. Contributions

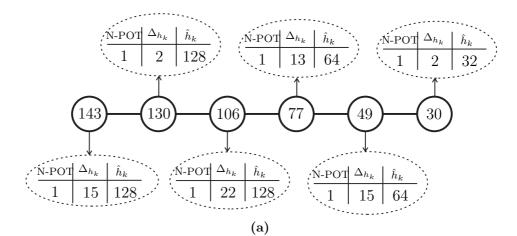

This work proposes a novel allocation scheme entitled coefficient deviation  $(\Delta_{h_k})$ . The proposed allocation scheme is used in the pre-processing stage to assure faster computation time for optimization problems such as polynomial programming and mixed integer linear programming. The preliminary idea was published in 2008 [1]. Moreover, a remarkable savings in the computation time of the FIR filter optimization problem has been achieved throughout extensive pre-processing analysis. A reduction by more than a factor of 400 was achieved by the proposed algorithm with the developed heuristic solver, published in 2012 [2]. On the system architectural level, a power aware combination criterion to combine direct-form and transposed-form FIR digital decimation filters which deliver a reduction in power consumption up to 15% compared to the conventional architecture was introduced and published in 2009 [3]. Further, a novel encoding scheme for shift-and-add multiplierless architectures entitled by nested multiplication was presented. The proposed scheme delivers a reduction in the number of full-adders of up to 25% compared to the state-of-the-art encoding schemes employing binary and canonic signed digit (CSD) representations.

On the application level, a power optimized digital front end architecture for narrow-band tunable FM digital receivers was proposed and synthesized. The proposed architecture achieved a reduction in power by more than 60% compared to the conventional architecture and was published in 2010 [4]. A comprehensive study has been carried out on ROM-based numerical controlled oscillators (NCO) which led to developing a design methodology for power optimized NCOs. Further, a numerical controlled oscillator was implemented<sup>1</sup> and a power reduction of 25% compared to the state-of-the-art architectures and 70% reduction compared to the conventional architecture.

### 1.4. Deliverables

- **MSD-toolbox**: a consolidate design framework for digital decimation filters based on MATLAB functions and scripts. The developed toolbox supports the design, optimization and implementation<sup>2</sup> of generic multi-stage decimation filters. The MSD-toolbox employs state-of-the-art design methodologies to assure efficient and reliable implementation of the decimation filter. Further, the toolbox integrates a wide set of attributes to enhance the optimization of the decimation filter.

- VHDL IPs: a set of RTL-based soft intellectual properties (IPs) have been developed and synthesized for ASIC and FPGA to facilitate the verification of the proposed power optimization methodologies. The delivered IPs are:

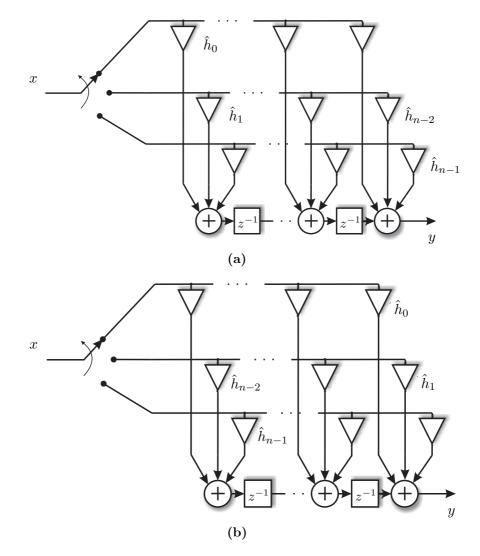

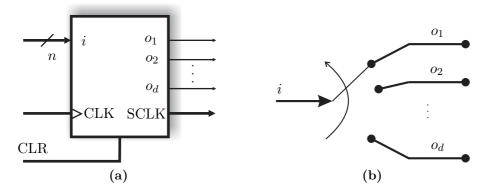

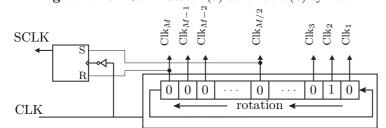

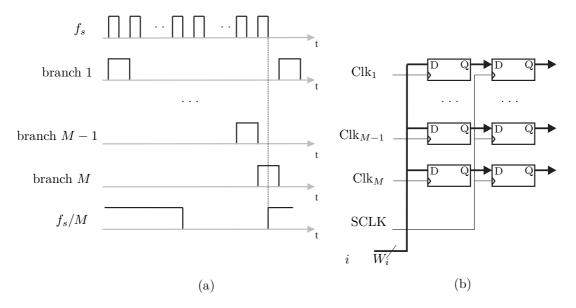

- PPD a Polyphase Decimation filter employing direct-form and transposedform structures.

- CIC a Cascaded Integrator Comb filter employing non-pipelined and pipelined architectures.

- NCO a Numerical Controlled Oscillator employing  $\pi/2$  or  $\pi/4$  sinusoidal symmetry and piecewise linear approximation.

$<sup>^{1}</sup>$ RTL synthesis + FPGA prototype

$<sup>^{2}</sup>$ RTL synthesis + place-and-route

DFE - a Digital Front End module employing a quadrature mixer, complex mixer, decimation stage, numerical controlled oscillator, and a digital control word.

## 2. Sigma Delta ADCs

#### 2.1. Introduction

This chapter gives a brief review of decimation filtering fundamentals. Primarily, survey summarizing the state-of-the-art analog-to-digital converters (ADCs) is given. The predominance of sigma delta ( $\Sigma\Delta$ ) analog-to-digital converter for high conversion accuracy and low power applications is stated afterwards. Detailed explanations on the fundamentals for  $\Sigma\Delta$  modulation is given in [5], [6], [7]. Next, several classifications of Sigma Delta modulators is presented. Further, a review of the decimation fundamentals and classifications is exhibited.

### 2.2. Need of Data Converters

The aggressive scaling of integrated circuit technology, has enabled binary computations to be performed by very complex data applications with low energy levels and higher speed [8], [9]. Digital circuits are robust and every year the speed and density of digital circuits are increased, leading to the dominance of digital integrated circuits in a wide range of applications [5]. Recently, digital signal processing and computing are the main drivers in modern electronic systems [9]. Though, analog circuits can benefit from technology scaling, analog circuits suffer from several limitations. Those limitations are defined by the analog design octagon [10]. Therefore, designers lean toward a system with minimum analog components. Since, real life signals remain analog, data converters are needed to interface with digital signal processing cores [5], [9].

### 2.3. Survey of Analog-to-Digital Converters

The analog to digital converters (ADCs) have progressed greatly in the last two decades [8]. ADCs can be classified into two main categories: Nyquist-rate and oversampled converters. Nyquist-rate ADCs individually convert each analog input word into a digital output sample, without reference to earlier inputs. Nyquist-rate ADCs can be classified based on the conversion algorithm used into Flash (parallel), successive approximation (Serial), Interpolating (Counting) and Pipeline [11]. Oversampling converters use a sample frequency much higher than the Nyquist

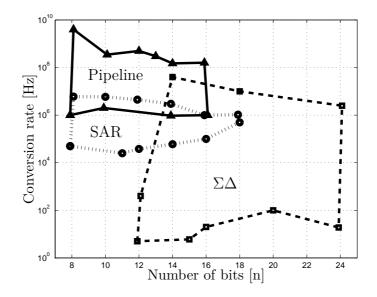

Figure 2.1.: Resolution and conversion frequency for more than 500 commercial ADC [8].

frequency of the signal being converted [6].

A learning methodology for ADCs was presented in [8], towards understanding the ADCs functionality and working fundamentals. Furthermore, a quantitative study for the state-of-art ADCs was presented in [12], which examines where ADCs are and where they are headed in terms of enabling performance. This study has examined several performance characteristics for data converters and examined their effect on system performance. The study concluded that, "However, it is clear that despite a general lag behind advances in digital processing, ADCs are nonetheless rapidly improving in all areas of figures-of-merit and will continue to do so, at least in the foreseeable future" [12]. Moreover, a quantitative survey for ADCs is posted on [13], considering various figures-of-merit and design parameters.

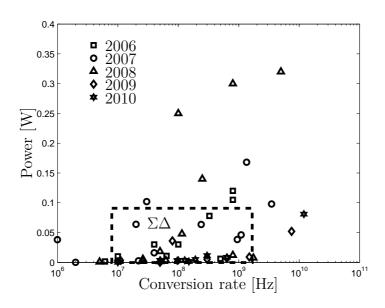

Figure 2.1 [8] presents the region of operation for the state-of-the-art ADCs in terms of conversion rate. It shows that, Sigma Delta ( $\Sigma\Delta$ ) ADCs provides the highest resolution while still achieving high speed [8]. Figure 2.2 shows power consumption in the state-of-the-art ADCs in terms of conversion rate. The power results in the figure are for Nyquist (SAR, Flash and Pipeline) and oversampling ( $\Sigma\Delta$ ) ADCs. The power consumption for decimation is not included for  $\Sigma\Delta$  ADCs. The figure reveals the contribution of  $\Sigma\Delta$  ADCs for low power and moderate to high speed applications [13].

### 2.4. Sigma Delta ADC

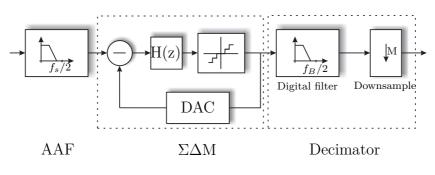

Oversampling converters have become very popular during the last decade. Figure 2.3 shows the block diagram of an oversampling  $\Sigma\Delta$  ADC that includes antialiasing filter (AAF), sigma delta modulator ( $\Sigma\Delta$ M), and decimation filter (digital

Figure 2.2.: Power consumption and conversion frequency for state-of-the-art ADCs, survey 2006-2010 [13].

filter+downsample), where  $f_s$  is the sampling frequency,  $f_B$  is the maximum signal frequency, OSR is the oversampling ratio defined by  $f_B = f_s/2$ OSR, and M is the decimation factor for downsampling. The AAF prior the  $\Sigma\Delta M$  is used to remove the out-of-band noise to prevent it from aliasing back by oversampling. The  $\Sigma\Delta M$ , known also as the noise shaping modulator, shapes the quantization noise by having a small fraction of the quantization noise within the band of interest and spreading most of it to the out-of-band range. The modulator consists of a loop filter H(z), a quantizer (single or multi-bit), and a feedback digital-to-analog converter (DAC).

#### 2.4.1. Sigma Delta Modulator Classifications

Sigma Delta modulators ( $\Sigma\Delta Ms$ ) are classified according to different criteria such as topology, implementation, structure, and architecture. The choice of the mod-

Figure 2.3.: Sigma Delta ADC block diagram.

|            |                                                                                                            | $\Sigma \Delta$                                                                  | ΔMs                                                                                                     |                                                                                                                    |  |  |

|------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

|            | Single                                                                                                     | •                                                                                | MASH                                                                                                    | Multi-bit                                                                                                          |  |  |

|            | Low order FB                                                                                               | High order FF                                                                    |                                                                                                         |                                                                                                                    |  |  |

| Advantages | <ul> <li>Simple circuitry</li> <li>High DR</li> <li>Stability</li> <li>Better<br/>anti-aliasing</li> </ul> | <ul> <li>Large SNR for<br/>low OSR</li> <li>Smaller<br/>noise pattern</li> </ul> | <ul> <li>Large SNR for<br/>low OSR</li> <li>High DR</li> <li>Guaranteed<br/>stability</li> </ul>        | <ul> <li>Large SNR for<br/>low OSR</li> <li>Better stability</li> <li>Smaller noise<br/>pattern</li> </ul>         |  |  |

| Drawbacks  | <ul> <li>High OSR</li> <li>Presence of noise patterns</li> </ul>                                           | <ul> <li>Conditional stability</li> <li>Need low gain integrator</li> </ul>      | <ul> <li>Complex digital<br/>circuitry</li> <li>Sensitivity to<br/>circuit<br/>imperfections</li> </ul> | <ul> <li>Complex<br/>analog and<br/>digital circuitry</li> <li>Sensitivity to<br/>DAC<br/>non-linearity</li> </ul> |  |  |

| Remarks    | • Preferred for<br>low power<br>design                                                                     |                                                                                  | • Preferred for<br>bandwidth<br>demanding<br>applications                                               | • Preferred for<br>bandwidth<br>demanding<br>applications                                                          |  |  |

Table 2.1.: Summary of Sigma Delta topologies advantages and drawbacks [6], [7], [18] $\Sigma \Delta Ms$

ulator depends on the performance requirements and the application. Some applications require high speed and high resolution converters. Other applications require low power with moderate resolution.

$\Sigma\Delta$ Ms have several topologies known as single loop feedback, single loop feedforward, and cascaded or Multi-Stage Noise Shaping (MASH). On the one hand, single loop, low order  $\Sigma\Delta$ Ms with feedback topology exhibits a stable modulator with simple circuitry suitable for low power applications but with low signal-tonoise ratio (SNR). On the other hand, high order, single loop  $\Sigma\Delta$ Ms with feedforward topology exhibits higher SNR but suffers from conditional stability. Although, single bit quantizer affords simple circuitry, multi-bit quantizer provides large SNR with associated complex circuitry. However, a modulator with a multibit quantizer with a single bit in feedback combines the advantages of single bit and multi-bit quantizers [14]. A detailed study for  $\Sigma\Delta$ M topologies can be found in [15]. A detailed study for state-of-the-art MASH  $\Sigma\Delta$ Ms is given in [16]. While, a brief comparative study has been carried out in [17].

$\Sigma\Delta Ms$  are implemented by continuous-time (CT) or discrete-time (DT) circuitry.

| Lowpass<br>NB/WB                |                                       | Bandpass<br>NB/WB/Tunable                                         |

|---------------------------------|---------------------------------------|-------------------------------------------------------------------|

| Single Loop<br><sub>FB/FF</sub> |                                       | $\begin{array}{c} \rm Cascaded/MASH\\ {}_{\rm FB/FF} \end{array}$ |

| $\operatorname{CT}$             |                                       | DT                                                                |

| Single-bit                      | Multi-bit with<br>single-bit feedback | Multi-bit                                                         |

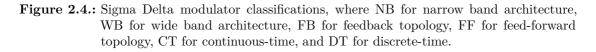

CT  $\Sigma\Delta$ Ms have smaller area than their DT counterparts. Contrary to a CT modulator, and they can operate at high clock speed with less power consumption [18]. On the other hand, DT  $\Sigma\Delta$ Ms achieve excellent matching of the time constants in the modulator [18]. Major advantages of the CT over the DT are the AAF effect and the low power. Discrete-time system can be mapped into continuoustime system by the inverse transformation. Moreover, a DT simulation for the CT  $\Sigma\Delta$ Ms is efficiently done by using the DISCO MATLAB toolbox [19]. A detailed analysis for CT  $\Sigma\Delta$ Ms can be found in [20]. A full study for CT  $\Sigma\Delta$ Ms can be found in [16], [21]. The  $\Sigma\Delta$ M is suitable for baseband applications (lowpass) as well as RF or IF applications (bandpass). Figure 2.4 summarizes the  $\Sigma\Delta$ M classifications. Table 2.1 summarizes the advantages and drawbacks for the different  $\Sigma\Delta$ M topologies.

A concise overview for  $\Sigma\Delta$  ADCs can be found in [22]. Moreover, a detailed explanations on the fundamentals of  $\Sigma\Delta$  ADCs are given in [5], [6], [7]. Furthermore, a quantitative analysis for  $\Sigma\Delta$  ADCs can be looked at [23]. Following, the digital filtering and downsampling stage, known as the decimation filter are discussed.

#### 2.4.2. Sigma Delta Decimation Filter

The  $\Sigma\Delta$  modulator output consists of the input signal together with noise components. However, there are different noise components within the modulator output. These noise components are the out-of-band noise, the modulation noise, the inband noise, and the quantization noise. The designers put a lot of effort to assure that the quantization noise is the dominant noise component, since the modulator react as a noise shaper for this particular noise component [5], [6], [7].

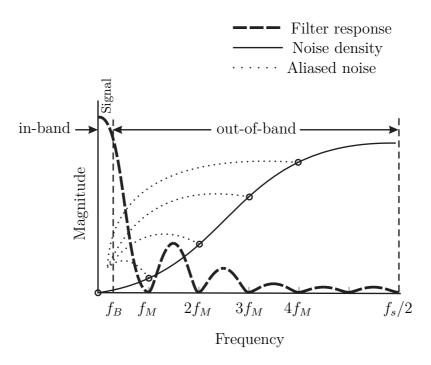

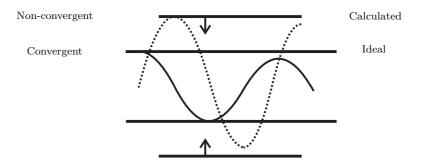

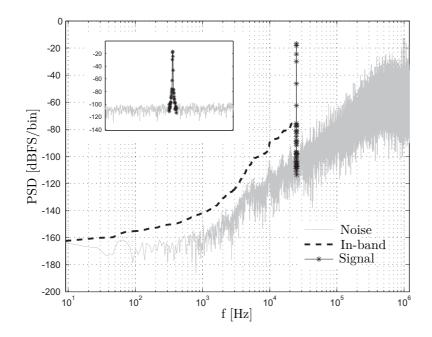

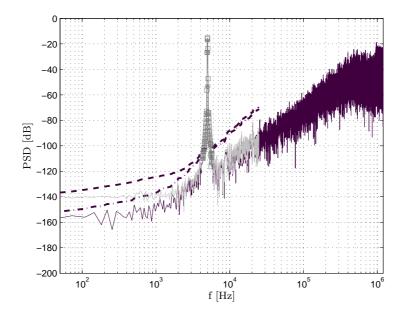

The noise shaper ( $\Sigma\Delta M$ ) shapes the noise in a way, so that a small fraction of the quantization noise lies within the in-band range (low frequencies) and it grows rapidly with increasing frequencies, as shown in Fig. 2.5 by the solid line. As shown in Fig. 2.5 the in-band range is defined as  $[0 - f_B]$ .

Figure 2.5.: Desired decimation response.

A filter stage is needed after the modulator to remove the out-of-band noise and to attenuate the folded noise. The folded noise is represented by the dotted lines in Fig. 2.5. This aliasing effect causes a noise penalty in the in-band range. Therefore, critical filtering is done in the digital domain where it is more robust against circuit imperfections [6].

A single filtering stage with such a steep response is not practically favorable. Consequently, filtering is performed by multiple filtering stages [24]. Oversampling converters relax the requirements of the analog circuitry, at the expense of faster, more complex digital circuitry [6]. After each filtering stage a downsampling stage exists, to decrease the sampling rate through removing the redundant part of the information due to the oversampling. Thus, a decimation stage consists of filtering stage in addition to downsampling stage. The decimation process is known in the literature as sampling rate conversion as well. The downsample process fundamentals are given in Appendix A.

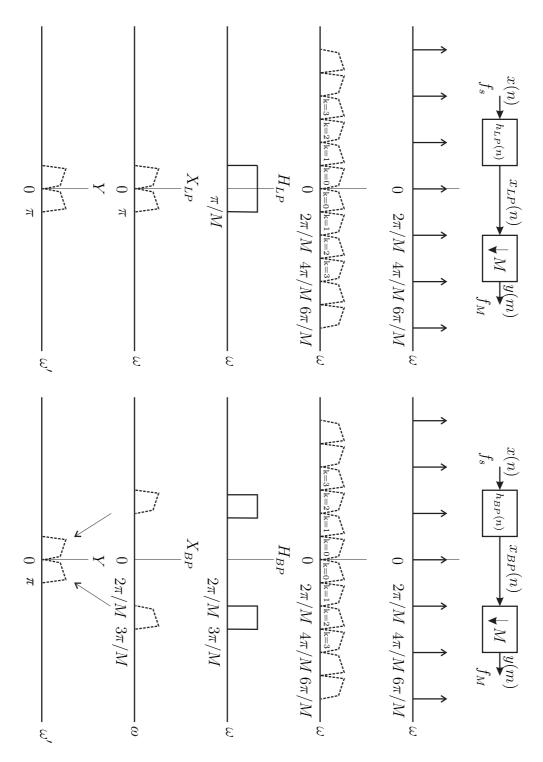

The decimation filter is categorized by architecture, implementation, topology, and structure. In accordance with  $\Sigma\Delta M$  architecture the decimation filter must be the same, whether lowpass or bandpass architecture. However, for a particular application a bandpass decimation filter is implemented using a downmixing stage followed by a lowpass decimation stage.

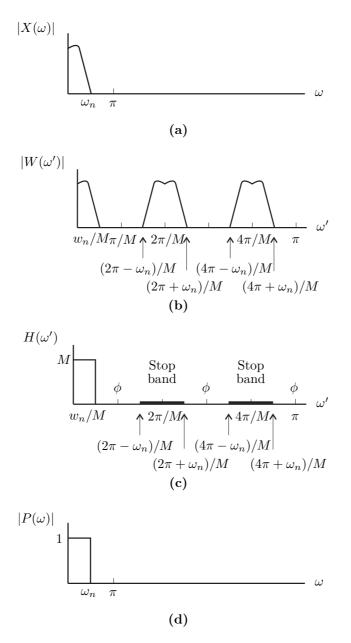

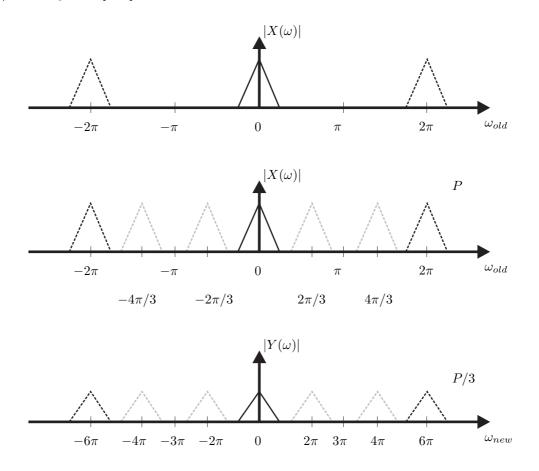

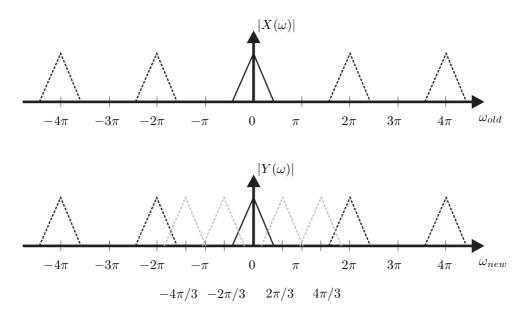

Figure 2.6 shows the spectral explanation of the decimation process. The  $\Sigma\Delta M$  output signal x(n) is first filtered to isolate the band of interest. Afterwards, the resulting signal is directly reduced in sampling rate by M. Bandpass and lowpass decimation filters are identical, with the exception of using bandpass filter  $(h_{BP})$  rather than lowpass filter  $(h_{LP})$ , as shown in Fig. 2.6. Sampling rate conversion

| Frequency Response |                             |  |  |  |  |  |

|--------------------|-----------------------------|--|--|--|--|--|

| Lowpass Bandpass   |                             |  |  |  |  |  |

| Impuls             | se Response                 |  |  |  |  |  |

| FIR                | FIR IIR                     |  |  |  |  |  |

| Topology           |                             |  |  |  |  |  |

| Direct-form        | Direct-form Transposed-form |  |  |  |  |  |

| St                 | ructure                     |  |  |  |  |  |

| PPD                | PPD CIC                     |  |  |  |  |  |

| Implementation     |                             |  |  |  |  |  |

| HB MB              |                             |  |  |  |  |  |

| Table 2.2.: | Decimation | filter | classifications |

|-------------|------------|--------|-----------------|

|             |            |        |                 |

process (decimation) can be regarded as a modulation process, as the spectrum of the signal x(n) is located at harmonics of the sampling frequency, which is translated back to the baseband [25], [26], [27]. Hence, the downsampling process is an implicit down mixing process [25], as shown in Fig. 2.6 by the translation of the bandpass signal  $X_{BP}$  to baseband signal Y after downsampling.

The state-of-the-art decimation structures are the polyphase decomposition (PPD) filter, the half-band (HB) filter, and the cascaded integrator comb (CIC) filter.

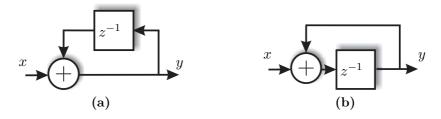

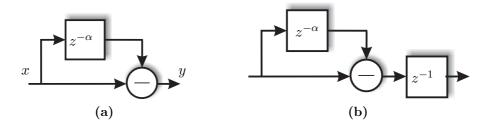

The transposed-form topology is often used for multiple constant multiplication (multiplier block) optimization, hence the filter coefficients form a common space. Hence, FIR filters have a flat group delay response [24], as commonly used in audio applications. On the other hand, IIR filters are preferable in sensor applications such as in gyroscopes. Table 2.2 summarizes the decimation filter classifications. It should be noted that only the topologies and structures for the FIR filters are presented. The advantages and drawbacks of each FIR structure are discussed in more details in chapter 7.

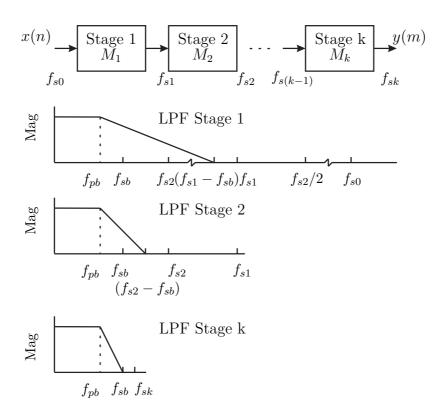

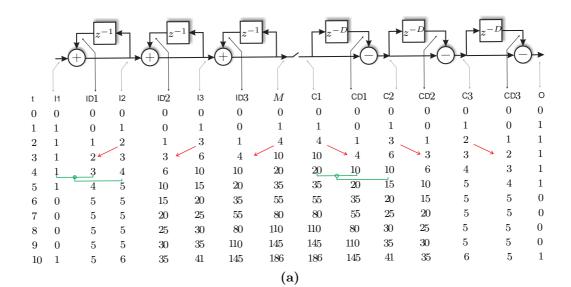

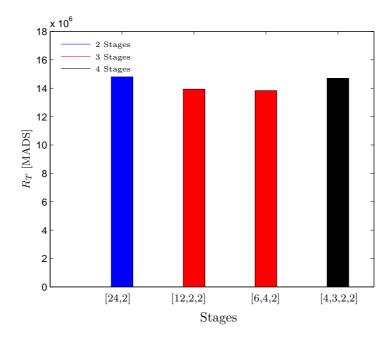

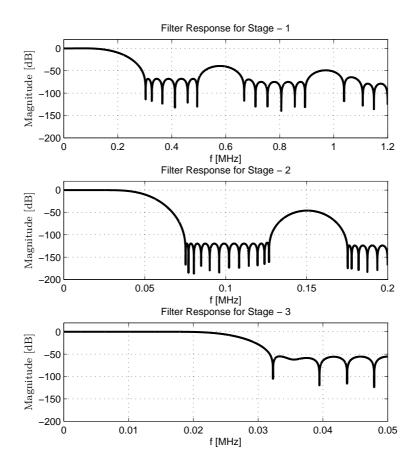

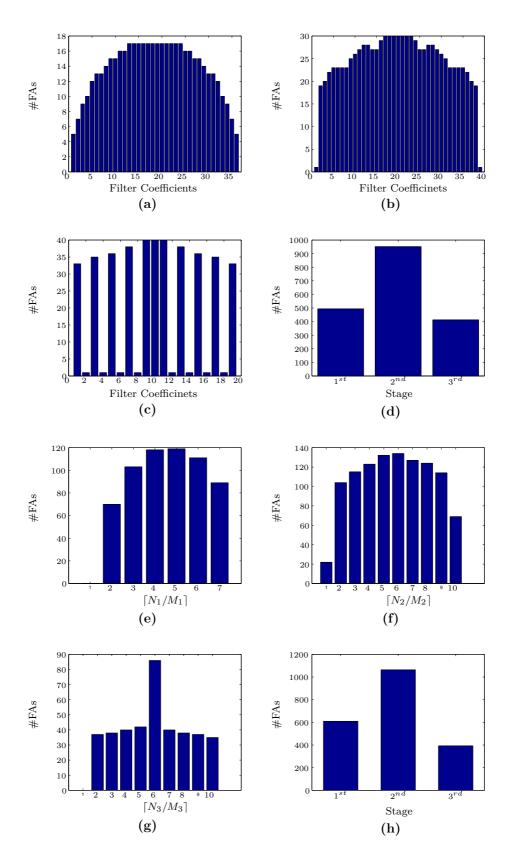

Decimation filter efficiency is directly related to the decimation filter type, order and the architecture used in the implementation [7]. The cascade of two or more decimation stages is described for reduction in filter arithmetic [24]. Whereas, the sampling rate is reduced gradually resulting in much less filtering requirements on the lowpass filters at each stage [28]. A procedure for the proper choice for decimation factor of the stages was presented in [24] and [28]. Detailed analysis for multistage decimation filtering is given in [25], [26], [28]. Numerical examples for multistage decimation are given in [7], [25]. Figure 2.7 shows the multi-stage decimation network and the frequency specifications for *i*-stage, where x(n) is the  $\Sigma\Delta M$  output, y(d) is the decimation filter output. Illustratively, the first lowpass filter stage (LPF) has an input sampling rate  $f_{s0}$ , output sampling rate  $f_{s1} = f_{s0}/M_1$ , passband frequency  $f_{pd}$  remains the same, and stopband frequency  $f_{sb} = f_{s1} - f_{sb}$  which is very relaxed in comparison to  $f_{sb}$ . Consequently, this relaxed filter specifications leads to less filter order.

Figure 2.6.: Decimation spectral.

The overall decimation factor M is given as

$$M = \prod_{i=1}^{k} M_i$$

$$= f_{s0}/f_{sk}$$

(2.1)

The intermediate sampling frequencies are given by

$$f_{si} = \frac{f_{s(i-1)}}{M_i}, \qquad i = 1, 2, \cdots$$

(2.2)

Figure 2.7.: Typical spectra for multi-stage decimation filter, where  $M_i$  is the decimation factor for stage i,  $f_{pd}$  is the passband frequency,  $f_{sb}$  is the stopband frequency,  $f_{s0}$  is the initial sampling frequency,  $f_{sk}$  is the final sampling frequency with intermediate sampling frequencies  $f_{s1}, f_{s2}, \dots, f_{s(i-1)}$ .

| 0                             |

|-------------------------------|

| IIR                           |

| No exact linear phase         |

| Critically stable             |

| Poor quantization properties  |

| Low order efficient filters   |

| Less efficient for decimation |

|                               |

| <b>Table 2.3.:</b> FIR vs | . IIR digital filters |

|---------------------------|-----------------------|

| FIR                       | IIR                   |

| oor phoso                 | No ovact linear ph    |

| Table 2.4.: | Digital | filter | $\operatorname{design}$ | and | implem | en | tati | on | parameters |

|-------------|---------|--------|-------------------------|-----|--------|----|------|----|------------|

|             |         |        |                         |     |        | ι. |      |    |            |

| Design Parameter            | Symbol        |

|-----------------------------|---------------|

| Passband frequency          | $f_{pb}$      |

| Stopband frequency          | $f_{sb}$      |

| Passband ripples            | $\delta_{pb}$ |

| Stopband ripples            | $\delta_{sb}$ |

| Stopband attenuation        | $A_{sb}$      |

| Sampling frequency          | $f_s$         |

| Filter order                | N             |

| Filter coefficients         | $h_k$         |

| Quantization bit-width      | Q             |

| number of decimation stages | k             |

| decimation factor           | M             |

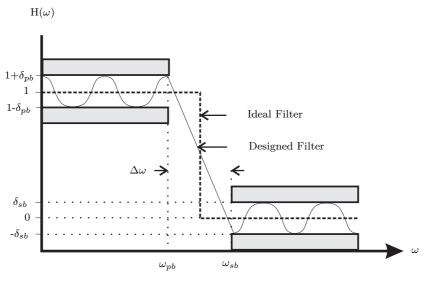

#### 2.5. Decimation Filter Design Parameters

Sampling rate converters involve classical filters, whether lowpass or bandpass, for band selection and noise filtering [29]. The tendency towards digital signal processing (DSP) is increasing and extending simultaneously with the continuous advances in silicon technology [5]. Therefore, digital filters are the main concern for this work. Digital filters can be implemented either as a finite impulse response (FIR) or infinite impulse response (IIR) filter. Table 2.3 summarizes the advantages and disadvantages for both FIR and IIR digital filters [29]. This work considers only FIR decimation filter. Digital FIR filters can be designed using several techniques such as windowing and equiripple techniques. This work considers the Parks-McClellan equiripple algorithm for designing an optimal FIR filter. The filter design process imports the design specifications and exports the implementation parameters. The filter design specifications and implementation parameters are given in Table 2.4. The resultant filter coefficients are with infinite precision. Consequently, the filter coefficients are presented in fixed precision format for practical hardware implementation. Subsequently, the precise number of bits required for representing the filter coefficients in fixed precision has to be determined, which is defined by Q.

### 2.6. Summary

The primary purpose of the decimation filter is filtering the noise aliased back into the in-band range due to oversampling. Furthermore, the secondary purpose is to transform a high rate narrow bit-width data stream of the  $\Sigma\Delta M$  to low rate wide bit-width data stream (high resolution). Decimation is performed by multiple cascaded decimation stages.

# 3. Low Power Design Aspects

# 3.1. Introduction

This chapter addresses concisely the components of power consumption in VLSI circuits, power optimization at multiple design levels, power optimization approaches at each individual design level, and power analysis employing modern electronic design automation tools (EDAs).

Figure 3.1.: VLSI design trades-off.

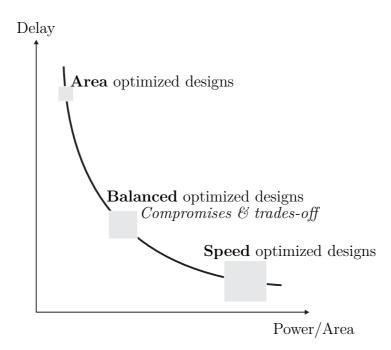

Low power design has become a major concern in VLSI circuit design, due to the continuous advances in silicon technology. The aggressive shrinking in the silicon technology has increased the gate density and the clock frequency [9]. But power dissipation rises simultaneously with increasing clock frequencies. Persistently, a power speed trades-off or power area trades-off is a crucial issue in modern VLSI design. On the one hand, small area designs suffer from drastic latency [30], [31], as shown in Fig. 3.1. On the other hand, fastest designs suffer from drastic power and area overhead [30], [31], as shown in Fig. 3.1. Therefore, the major trend for

Figure 3.2.: Components of power consumption in VLSI circuits.

designers is to balance the trade-off while meeting the performance requirements. The power dissipation can be scaled from one CMOS technology node to the next based on dedicated scaling algorithms. Power dissipation is scaled according to constant voltage scaling by  $\alpha$  [32], where  $\alpha$  is the ratio between the CMOS technology nodes. On the other hand, power dissipation is scaled by  $1/\alpha^2$  according to constant field scaling [32].

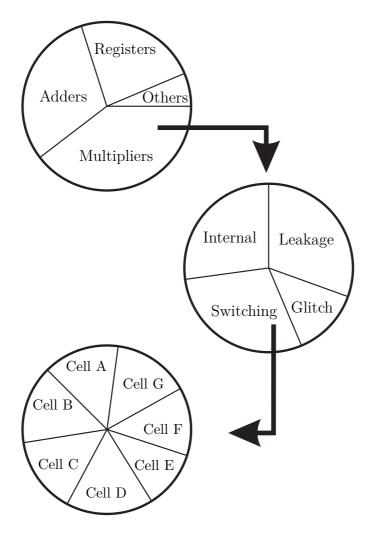

## 3.2. Sources of Power Dissipation

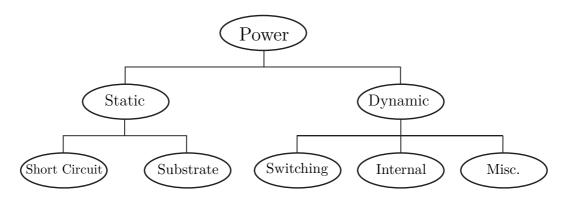

Power consumption is a process specific criterion, since each technology has different power profile characteristics. Therefore, at first, the components of power consumption in VLSI circuit are defined. The major components of power dissipation in VLSI circuit are briefly summarized in Fig. 3.2, mathematically analyzed by (3.1-3.6), and modeled as shown in Fig. 3.3. The total power  $(P_{Total})$  consumption of a cell is defined by (3.1).

$$P_{Total} = P_{Static} + P_{Dynamic} \tag{3.1}$$

The dynamic power  $(P_{Dynamic})$  is the power dissipated when the circuit is active. In other words, when the voltage of a net is changing or switching between high and low [33], [34]. The dynamic power components of the total power are depicted in (3.2).

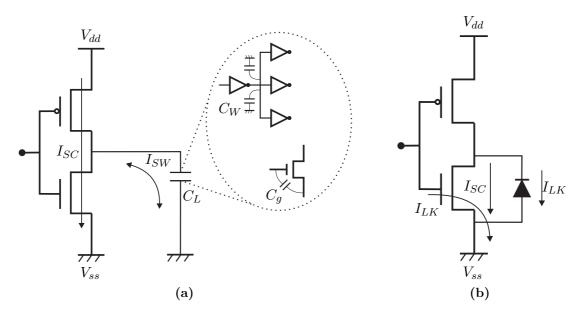

$$P_{Dynamic} = P_{Switching} + P_{Internal} + P_{Misc} \tag{3.2}$$

where the switching power  $(P_{Switching})$  is the power dissipated by charging and discharging a load capacitance  $(C_L)$  [33], [34]. The load capacitance is defined at the output node of the cell by the sum of wire  $(C_W)$  and gate capacitances  $(C_g)$ . The process of charging and discharging the output load capacitance of a cell is emulated by the switching current  $(I_{SW})$  shown in Fig. 3.3.a. The switching power is proportional to the supply voltage  $(V_{dd})$ , the load capacitance  $(C_L)$ , the net toggle rate  $(T_R)$ , and the clock frequency (f), as depicted in (3.3). Equation 3.3

Figure 3.3.: Modeling of power consumption components (a) dynamic (b) static.

reveals the dominance of the supply voltage  $V_{dd}$  and the clock frequency f in reducing dynamic power dissipation by reducing either of them or both.

$$P_{Switching} \propto T_R \times C_L \times {V_{dd}}^2 \times f_s \tag{3.3}$$

The internal power  $(P_{Internal})$  is the power dissipated within a cell itself by charging and discharging internal capacitance. Moreover, the momentary short circuit between the P and N transistors dissipates an amount of power considered also as internal power, emulated by the short circuit current  $(I_{SC})$  shown in Fig. 3.3.a. The internal capacitance is a function of the input transition time  $(t_T)$  and the output capacitance  $(C_o)$  [33], [34].

$$P_{Internal} \propto F(t_T, C_o) \tag{3.4}$$

Moreover, there are the power dissipated by the clock tree and the internal glitches. This is modeled as miscellaneous components of power dissipation. The miscellaneous power consumption can be defined by

$$P_{Misc} = P_{Clock} + P_{Glitch} \tag{3.5}$$

Whereas, the static power  $(P_{Static})$  is the power dissipated by the circuit when it is inactive [33], [34]. The static power components of the total power consumption is depicted by

$$P_{Static} = P_{ShortCircuit} + P_{Substrate} \tag{3.6}$$

The short circuit power ( $P_{ShortCircuit}$ ) is the power dissipated by the source-todrain sub-threshold leakage [33], [34]. The source-to-drain short circuit leakage is emulated by the short circuit current ( $I_{SC}$ ) shown in Fig. 3.3.b. The substrate power ( $P_{Substrate}$ ) is the power dissipated in the diffusion layer and the substrate. The power dissipated by the bulk leakage is emulated by the bulk leakage current ( $I_{LK}$ ) shown in Fig. 3.3.b.

Figure 3.4.: Design levels.

# 3.3. Power Optimization Approaches

A reduction of the power dissipation can be achieved at several levels in the design process, as shown in Fig. 3.4. The design process is categorized into three major levels: the system level, the register transfer level (RTL), and the gate level (also known as physical level). The system level is the highest design level, where one can model or define the design abstractly, algorithmically, or architecturally. On the RTL level (front-end) the designer has to have a full awareness of the design details. The physical or the gate level (back-end) is the lowest level in the design hierarchy and the most sophisticated level. Each level of design has different power optimization approaches with certain impact on the reduction of power consumption, whether static or dynamic power dissipation. Not all optimization techniques may be suitable for the design, so that the designer has to assess the different techniques for complexity, risk, and cost [30]. Excessive effort is spent on the power optimization at the gate level for slight reduction in the power consumption (if the leakage power is not important), as shown in Fig. 3.4. Table 3.1 exhibits several power optimization approaches at the individual design levels and their impact on power reduction. Apprehensively, the gate level power optimization approaches have a direct dominant effect on the leakage power consumption reduction. Thus, the back-end power optimization approaches is used after exhausting all the approaches for dynamic power reduction [30]. Otherwise, where the reduction of the leakage power dissipation is of importance. For significant power saving, a combination of two or more optimization approaches is preferable. As an example, combining clock gating and power gating proposed in [35] for optimizing both dynamic and leakage power. Moreover, controlling  $V_{dd}$  and  $V_{TH}$  simultaneously as proposed in [36] for optimizing both dynamic and leakage power.

Since, the physical level optimization methodologies are beyond the scope of this

| el     | Approach                      | Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Frequency scaling             | Dynamic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| System | $Multi-V_{dd}^{-1}$           | Dynamic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | Power efficient IPs           | Dynamic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

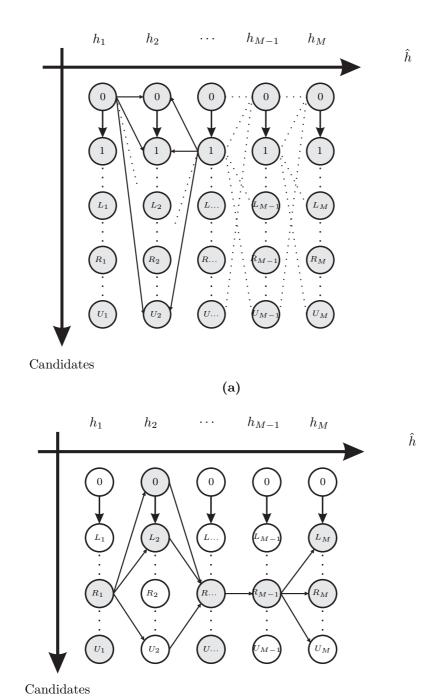

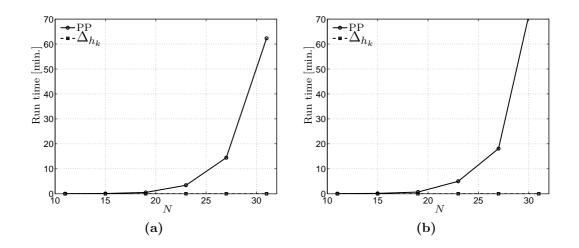

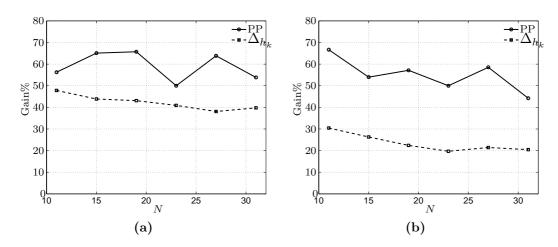

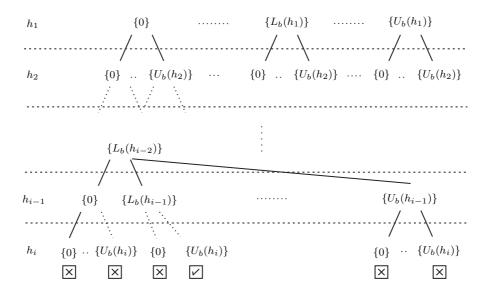

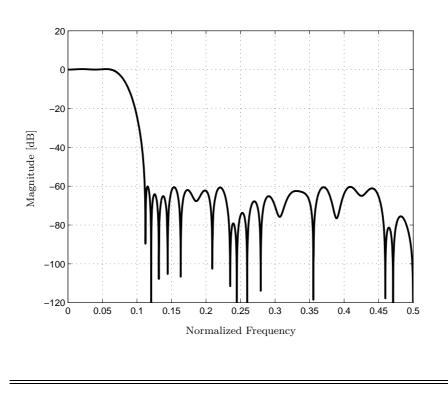

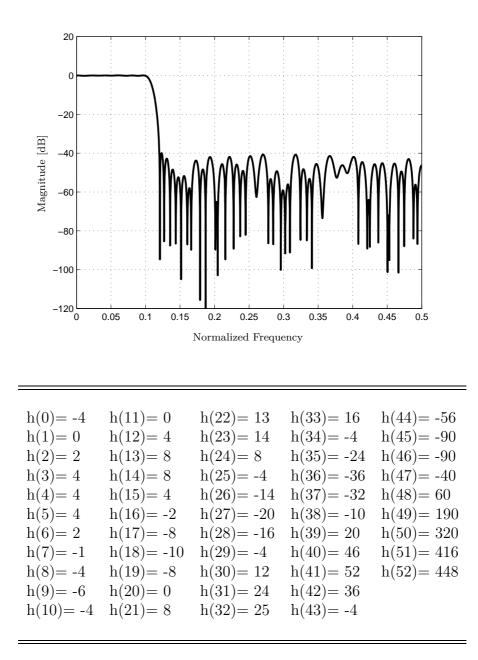

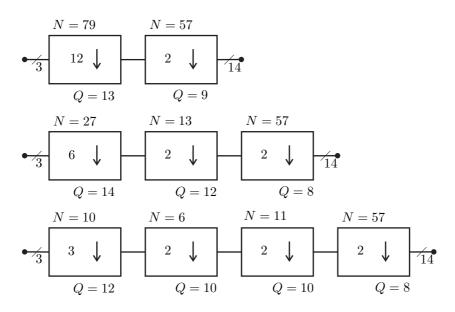

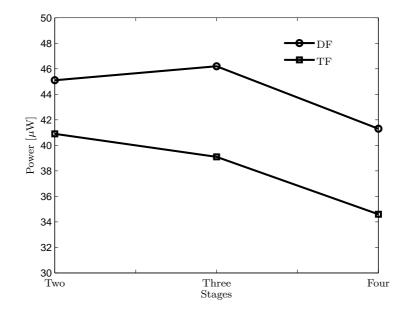

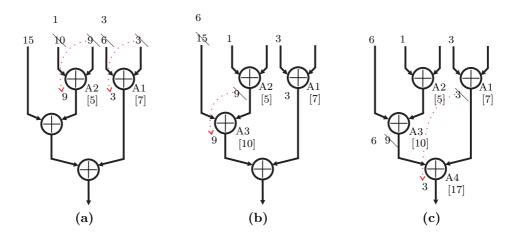

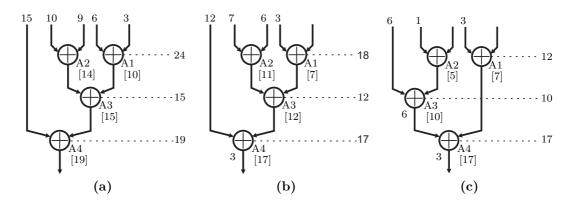

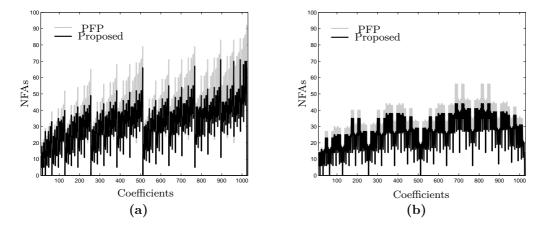

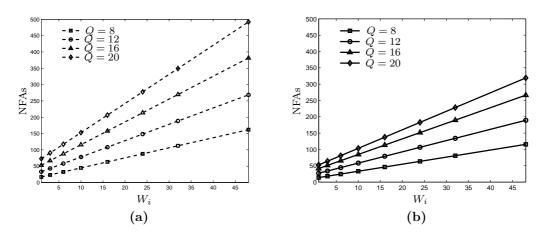

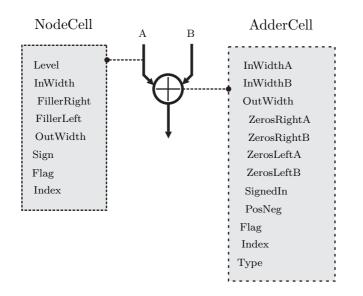

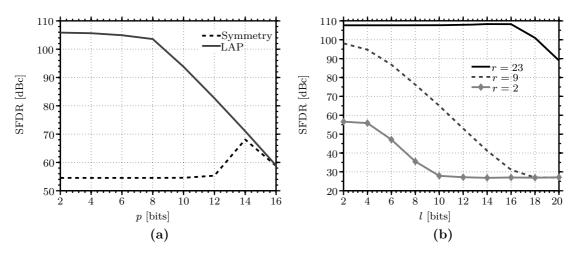

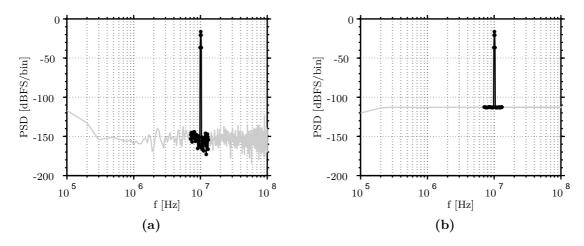

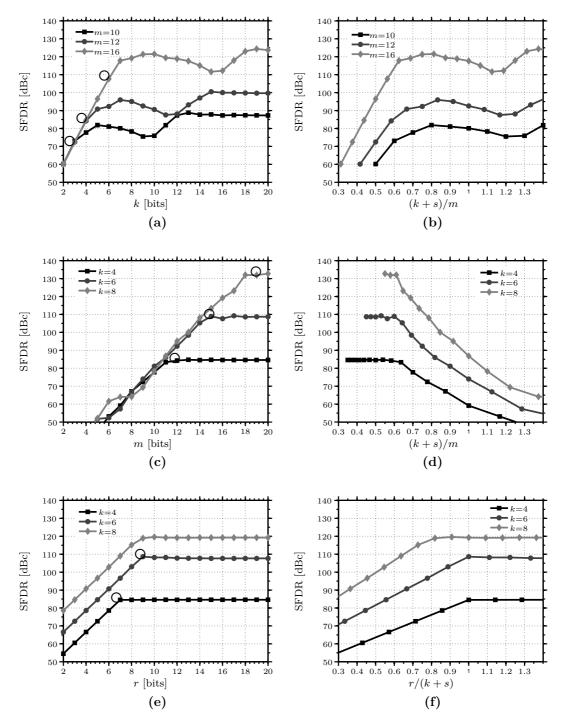

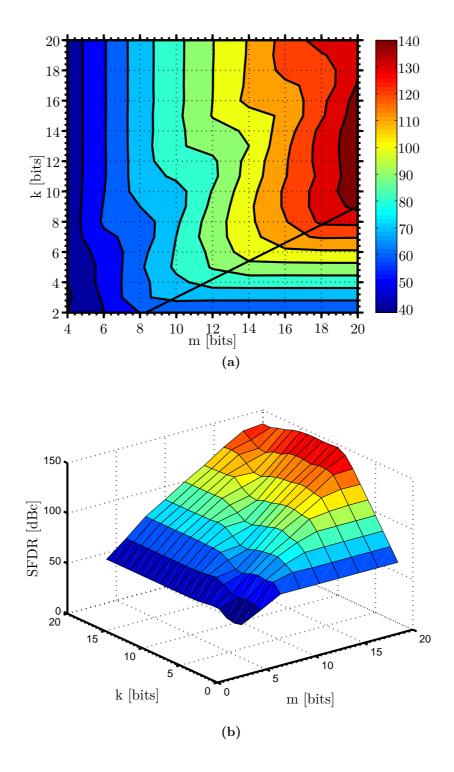

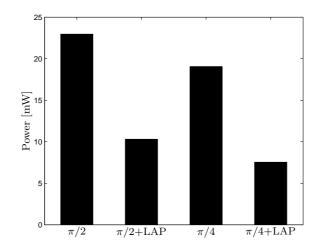

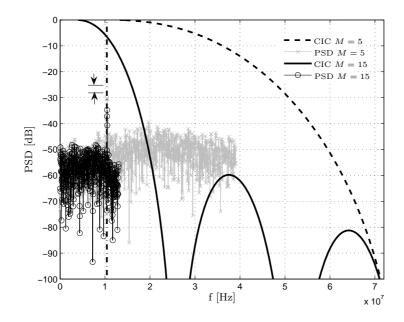

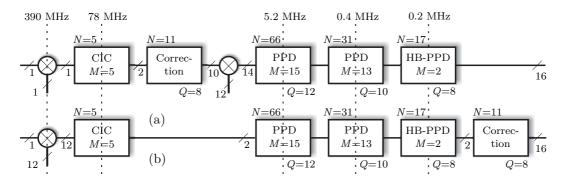

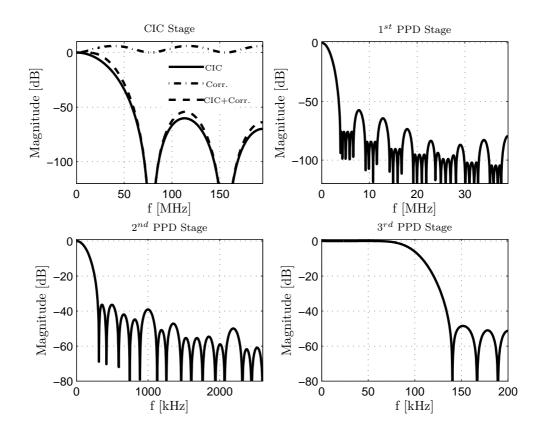

|        | Power optimization algorithms | Dynamic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |